6t Sram Bit Cell

Low power single bit line 6t sram cell with high read stability Tsmc’s 5nm 0.021um2 sram cell using euv and high mobility channel with Sram cells

Characteristics of 6T SRAM cell. | Download Scientific Diagram

A simple 6t sram cell. the cell is biased toward the 1-state by Static random-access memory (sram) Sram cmos 6t

Sram simulation 6t cell

7.3 6t sram cellConventional 6t sram cell Sram cell layout 6t high bit 5nm tsmc fig density assist euv mobility channel write using semiwikiCell sram 6t power stability bit single low line read high write.

Sram 6t register file 5nm node tsmc semiwiki conventionalSram cell. (a) conventional 6t sram cell. (b) new loadless 4t sram cell Sram cells unveiledStandard 6t sram cell. a) 6t sram cell working in standard 6t sram.

Sram 6t standard inverter

Sram 6t timing 10t consumption proposed operating principleCharacteristics of 6t sram cell. 6t sram6t-sram cell scaling trend fig. 2 : 45nm sram cells design rules fig.3.

Sram 6t conventionalSram 6t biased magnitude Conventional 6t sram cell [7]Sram 6t 4t cell cmos submicron technologies conventional 90nm 130nm.

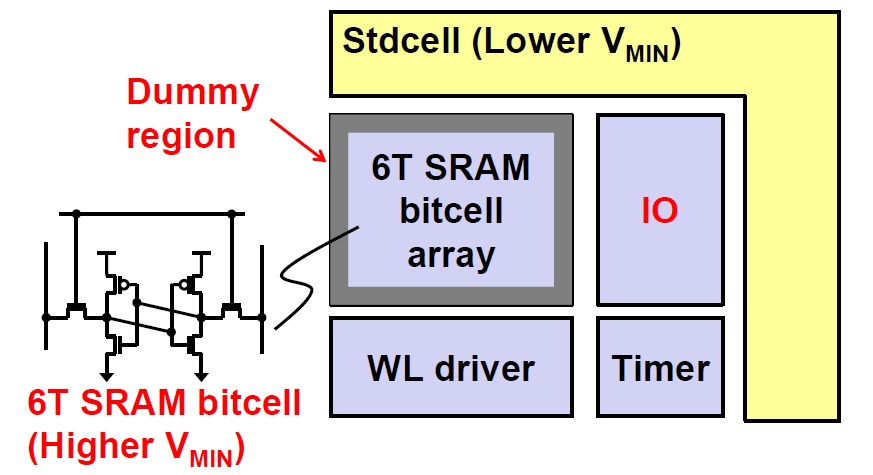

Register file design at the 5nm node

6t-cmos sram cell [8].Sram cell 6t vlsi dram lecture cmos introduction ee466 ppt powerpoint presentation precharge slideserve size (pdf) 6t-sram for low power consumptionSimulation result of 6t sram cell.

Conventional 6t sram cell.[4]6t 8t sram wikichip nmos comprising transistors Sram cell 6t cmos circuit transistor transistors6t sram.

![Conventional 6T SRAM Cell.[4] | Download Scientific Diagram](https://i2.wp.com/www.researchgate.net/publication/341908814/figure/download/fig1/AS:898687123329026@1591275115535/Conventional-6T-SRAM-Cell4.jpg)

Sram 6t 45nm scaling cells trend

Conventional sram 6t .

.

![6T-CMOS SRAM cell [8]. | Download Scientific Diagram](https://i2.wp.com/www.researchgate.net/publication/276489315/figure/fig1/AS:615055968198656@1523652178202/6T-CMOS-SRAM-cell-8.png)

Characteristics of 6T SRAM cell. | Download Scientific Diagram

A simple 6T SRAM cell. The cell is biased toward the 1-state by

SRAM Cell. (a) Conventional 6T SRAM Cell. (b) New Loadless 4T SRAM Cell

TSMC’s 5nm 0.021um2 SRAM Cell Using EUV and High Mobility Channel with

Static Random-Access Memory (SRAM) - WikiChip

![Conventional 6T SRAM Cell [7] | Download Scientific Diagram](https://i2.wp.com/www.researchgate.net/profile/Shilpi_Birla/publication/271304374/figure/download/fig1/AS:601138848100352@1520334078583/Conventional-6T-SRAM-Cell-7.png)

Conventional 6T SRAM Cell [7] | Download Scientific Diagram

Register File Design at the 5nm Node - Read mroe on SemiWiki

Low Power Single Bit line 6T SRAM Cell With High Read Stability